:

### II B. Tech II Semester Regular Examinations, June/July - 2022 DIGITAL ELECTRONICS

(Electrical and Electronics Engineering)

| Tiı | ne: 🤅 | 3 hours Max. Marks: 70                                                                                                                                            |      |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|     |       | Answer any <b>FIVE</b> Questions each Question from each unit<br>All Questions carry <b>Equal</b> Marks                                                           |      |

|     |       | UNIT-I                                                                                                                                                            |      |

| 1   | a)    | Convert the numbers $(0.3125)_{10}$ and $(1101.01)_2$ in base 8.                                                                                                  | [7M] |

|     | b)    | i. List the truth table of $F = xy + xy' + y'z$<br>ii. Draw logic diagrams to implement the Boolean expression<br>Y = A + B + B'(A + C')                          | [7M] |

|     |       | Or                                                                                                                                                                |      |

| 2   | a)    | Subtract the two numbers using 10's complement and 9's complement 6,428 – 3,409                                                                                   | [7M] |

|     | b)    | Represent the decimal number 5.137 in (i) BCDcode (ii) Excess-3 code                                                                                              | [7M] |

|     |       | UNIT-II                                                                                                                                                           |      |

| 3   | a)    | Simplify the following Boolean function, using three-variable maps:<br>$F(x, y,z) = \sum (0,2,6,7)$                                                               | [7M] |

|     | b)    | Explain a four-bit binary adder circuit with relevant diagram.                                                                                                    | [7M] |

|     |       | Or                                                                                                                                                                |      |

| 4   | a)    | Why is a four-bit adder circuit implemented with full adders? Explain the designing procedure?                                                                    | [7M] |

|     | b)    | Draw a circuit for a two's complement implementer using the 4-bit adder cum subtractor circuit.                                                                   | [7M] |

|     |       | UNIT-III                                                                                                                                                          |      |

| 5   | a)    | Design a 8 to 1 digital multiplexer? Also design with 4:1 MUX? Explain?                                                                                           | [7M] |

|     | b)    | Give the schematic circuit of a 2-to-4 binary decoder with an active-low enable input. Show the Truth Table.                                                      | [7M] |

|     |       | Or                                                                                                                                                                |      |

| 6   | a)    | Show a multiplexer is also a Boolean expression implementer.                                                                                                      | [7M] |

|     | b)    | Draw a block diagram of a PLA and explain it's architecture. Write differences between PLA and PROM. What is the design procedure of a PLA based circuit? UNIT-IV | [7M] |

| 7   | a)    | Explain the designing procedure of Master Slave JK Flip-Flop with suitable diagram?                                                                               | [7M] |

|     | b)    | Draw the waveforms to enter a serial data 11101into a SIPO shift register. Explain?                                                                               | [7M] |

|     |       | Or                                                                                                                                                                |      |

| 8   | a)    | What is a decade counter? Explain its circuit and write the applications of a decade counter?                                                                     | [7M] |

b) What do we mean by SIPO, PISO, PIPO and SISO Shift registers? Explain with [7M] timing diagram (i) shift left in each and (ii) shift right in each.

UNIT-V

- 9 a) Distinguish between a Transition table and Excitation table? Explain with an [7M] example.

- b) Define Finite State machine for the state table using JK Flip-Flop. [7M]

|               |                            | Inputs (AB) |    |    |  |

|---------------|----------------------------|-------------|----|----|--|

| Present state | 00                         | 01          | 10 | 11 |  |

| $(Q_1 Q_0)$   |                            |             |    |    |  |

| 00            | 01                         | 00          | 00 | 01 |  |

| 01            | 10                         | 00          | 00 | 10 |  |

| 10            | 11                         | 00          | 00 | 11 |  |

| 11            | 01                         | 00          | 00 | 01 |  |

|               | Next State $(Q_1 * Q_0 *)$ |             |    |    |  |

Or

- 10 a) What is the importance of reduction of number of states? What is the advantage of [7M] standard form for state tables? Explain with an example.

- b) Explain the design procedure of Asynchronous sequential circuits. [7M]

2 of 2

## II B. Tech II Semester Regular Examinations, June/July - 2022 DIGITAL ELECTRONICS

(Electrical and Electronics Engineering)

| Ti | me: (     | 3 hours Max. Marks: '                                                                                                                                                                                                                                                 | 70   |

|----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    |           | Answer any <b>FIVE</b> Questions each Question from each unit<br>All Questions carry <b>Equal</b> Marks                                                                                                                                                               |      |

|    |           | UNIT-I                                                                                                                                                                                                                                                                |      |

| 1  | a)        | Given the two binary numbers $X = 10101111$ and $Y = 10000101$ , perform the subtraction                                                                                                                                                                              | [7M] |

|    | b)        | (i) <i>X</i> - <i>Y</i> and (ii) <i>Y</i> - <i>X</i> by using 2's complement technique?<br>i. Express the Boolean function $F = xy + x'z$ as a product of maxterms<br>ii. Find the complement of $F = wx + yz$ ; then show that $FF' = 0$ and $F+F' = 1$<br><b>Or</b> | [7M] |

| 2  | a)        | Convert the following expressions into sum of products and product of sums:<br>i. $(AB + C'D)(B+C'D)$<br>ii. $Y' + r(r + r')(r + r')$                                                                                                                                 | [7M] |

|    | b)        | ii. $X' + x(x + y')(y + z')$<br>Draw the logic diagram to the following Boolean expressions without simplifying them:                                                                                                                                                 | [7M] |

|    |           | i. $BC'+AB+ACD$<br>ii. $(A+B)(C+D)(A'+B+D)$<br><b>UNIT-II</b>                                                                                                                                                                                                         |      |

| 3  | a)        | Simplify the following Boolean function, using three-variable maps:                                                                                                                                                                                                   | [7M] |

| 5  | <i>a)</i> | $F(x, y,z) = \sum (0,2.3,4,6)$                                                                                                                                                                                                                                        |      |

|    | b)        | Draw the circuit diagram of a 2-bit adder-subtractor and explain the function?                                                                                                                                                                                        | [7M] |

|    |           | Or                                                                                                                                                                                                                                                                    |      |

| 4  | a)        | Draw the block diagram of a full adder using two half adders and one OR gate.                                                                                                                                                                                         | [7M] |

|    | b)        | Simplify the following Boolean expression, using three-variable maps:<br>F(x,y,z) = xy + xy'z' + x'yz'                                                                                                                                                                | [7M] |

| _  |           | UNIT-III                                                                                                                                                                                                                                                              |      |

| 5  | a)        | Design a combinational circuit that will accomplish the multiplication of the 2-bit binary number $X_1 X_0$ by the 2-bit binary number $Y_1 Y_0$ . Is a two-level circuit the most economical? Justify?                                                               | [7M] |

|    | b)        | What is advantage of a PROM compared to the PLA and PALs? Explain.                                                                                                                                                                                                    | [7M] |

|    |           | Or                                                                                                                                                                                                                                                                    |      |

| 5  | a)        | Construct a 4 X16 decoder using five 2 X4 decoder modules. Explain with a neat schematic diagram.                                                                                                                                                                     | [7M] |

|    | b)        | What is the difference between a digital multiplexer and a digital demultiplexer?<br>Explain with an example?                                                                                                                                                         | [7M] |

|    |           | UNIT-IV                                                                                                                                                                                                                                                               |      |

| 7  | a)        | Define D and T flip-flop with the help of truth table? Also design the D and T flip-<br>flop using JK flip flop?                                                                                                                                                      | [7M] |

|    | b)        | Design a 4-bit asynchronous decade counter and draw the timing diagram.                                                                                                                                                                                               | [7M] |

|    |           | Or                                                                                                                                                                                                                                                                    |      |

### Code No:R2022022

| / |            |

|---|------------|

|   | <b>R20</b> |

|   | KZU        |

| 8  | a) | Draw the timing diagram of a 4-bit asynchronous counter and explain?                                                                                                       | [7M] |

|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | b) | Draw and explain briefly an Asynchronous Mod-12 counter?                                                                                                                   | [7M] |

|    |    | UNIT-V                                                                                                                                                                     |      |

| 9  | a) | Design a 5 state sequential machine whose sequential states are: 000, 001, 010, 110, 111, 000Assume initial state is 000.                                                  | [7M] |

|    | b) | Explain the design procedure of synchronous sequential circuits.                                                                                                           | [7M] |

|    |    | Or                                                                                                                                                                         |      |

| 10 | a) | Why state reduction is necessary in sequential circuit design? What are the different methods of state reduction? Explain implication table method of state reduction with | [7M] |

an example.

b) A synchronous counter is controlled by two input signals A and B. The counter does [7M] not operate, if A = 0 and B = 0. When A = 0 and B = 1, the counter operates as a mod four counter. If A=1 and B=0 the counter operates as a mod eight counter. Draw an FSM chart and design a circuit?

# II B. Tech II Semester Regular Examinations, June/July - 2022 DIGITAL ELECTRONICS

(Electrical and Electronics Engineering)

| Ti | me: | 3 hours Max. Marks                                                                                                                                                                                              | : 70 |

|----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    |     | Answer any <b>FIVE</b> Questions each Question from each unit<br>All Questions carry <b>Equal</b> Marks                                                                                                         |      |

|    |     | <br>UNIT-I                                                                                                                                                                                                      |      |

| 1  | a)  | i. Subtract $(12.50)_{10}$ from $(18.75)_{10}$ in binary using 1's complement method?<br>ii. Find the Gray Code number for the given 12-bit binary number<br>1 0 0 1 1 0 1 0 0 1 1 1 and explain the procedure? | [7M] |

|    | b)  | Implement the Boolean function $F = xy + x'y' + y'z$ with AND, OR and inverter gates                                                                                                                            | [7M] |

|    |     | Or                                                                                                                                                                                                              |      |

| 2  | a)  | Express the following sum-of -Products function $F(A,B,C,D) = \Sigma(3,5,9,11,15)$ in to POS form.                                                                                                              | [7M] |

|    | b)  | Show that the dual of the exclusive-OR is equal to its complement?                                                                                                                                              | [7M] |

|    |     | UNIT-II                                                                                                                                                                                                         |      |

| 3  | a)  | Simplify the following Boolean expression, using any two mapping techniques.<br>F(x,y,z) = xy + x'y'z' + x'yz'                                                                                                  | [7M] |

|    | b)  | Implement 8-bit adder circuit using full adders as the building blocks.                                                                                                                                         | [7M] |

|    |     | Or                                                                                                                                                                                                              |      |

| 4  | a)  | Simplify the Boolean function, $F(A,B,C,D)=\sum(0,1,4,5,7,15)+d(10,11,14)$ . Explain the procedure?                                                                                                             | [7M] |

|    | b)  | Draw the logic diagram of a half subtractor using NOR gates only.                                                                                                                                               | [7M] |

|    |     | UNIT-III                                                                                                                                                                                                        |      |

| 5  | a)  | Implement the following function using a multiplexer of proper size. $F(w, x, y, z) = \sum m(0, 1, 2, 3, 4, 9, 13, 14, 15)$                                                                                     | [7M] |

|    | b)  | $\overline{G}$ ive the logic circuit schematic to realize a BCD to decimal decoder.                                                                                                                             | [7M] |

|    |     | Or                                                                                                                                                                                                              |      |

| 6  | a)  | Design a 4 bit comparator using PROMs?                                                                                                                                                                          | [7M] |

|    | b)  | What is a difference between an encoder and a decoder? Explain with an example.                                                                                                                                 | [7M] |

|    |     | <b>UNIT-IV</b>                                                                                                                                                                                                  |      |

| 7  | a)  | What are the differences in a Master Slave JK FF, a Positive edge triggered JK-FF and a Negative edge triggered JK-FF?                                                                                          | [7M] |

|    | b)  | Draw a logic diagram of 4-bit ripple counter and explain its operation with timing diagram and sequence table. What modification is required to use as a decade counter?                                        | [7M] |

|    |     | Or                                                                                                                                                                                                              |      |

### Or

| Code | No: | R2022022 R20 SET -                                                                                                                                                              | 3    |

|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 8    | a)  | Write the difference between the following counters<br>(a) Synchronous counter and asynchronous counter<br>(b) Binary UP and binary DOWN counter                                | [7M] |

|      | b)  | Draw the logic circuit diagram of universal shift register and explain its operation with functional table.                                                                     | [7M] |

|      |     | UNIT-V                                                                                                                                                                          |      |

| 9    | a)  | Write design procedure of a finite state machine.                                                                                                                               | [7M] |

|      | b)  | Design a sequential circuit (finite state machine) for Table given below using D flip-<br>flops.Assume two inputs are A and B, outputs of the sequential circuit are outputs of | [7M] |

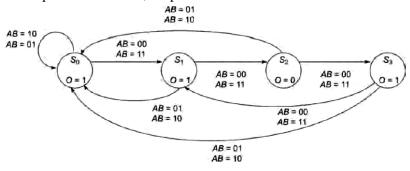

b) Design a sequential circuit (inite state machine) for Table given below using D inpflops. Assume two inputs are A and B, outputs of the sequential circuit are outputs of Dflip-flops, present state =S, Next State=S\*. Consider the four states of the sequential circuit are  $S_0=00$ ,  $S_1=01$ ,  $S_2=10$  and  $S_3=11$ .

|           | Inputs (AB)     |             |       |       |  |  |  |

|-----------|-----------------|-------------|-------|-------|--|--|--|

| Present   | 00              | 00 01 10 11 |       |       |  |  |  |

| state (S) |                 |             |       |       |  |  |  |

| $S_0$     | $S_1$           | $S_0$       | $S_0$ | $S_1$ |  |  |  |

| $S_1$     | $S_2$           | $S_0$       | $S_0$ | $S_2$ |  |  |  |

| $S_2$     | $S_3$           | $S_0$       | $S_0$ | $S_3$ |  |  |  |

| $S_3$     | $S_1$           | $S_0$       | $S_0$ | $S_1$ |  |  |  |

|           | Next State (S*) |             |       |       |  |  |  |

Or

- 10 a) Draw the state diagram and state table of a up-down counter. Design the Up-Down [7M] counter using Tflip-flops.

- b) The state diagram of a sequential circuit is given in Fig. Draw the state table for Fig. [7M] Assume two inputs are A and B, output is O.

## II B. Tech II Semester Regular Examinations, June/July - 2022 DIGITAL ELECTRONICS

(Electrical and Electronics Engineering)

|   |    | Answer any <b>FIVE</b> Questions each Question from each unit<br>All Questions carry <b>Equal</b> Marks                                                                                                               |     |

|---|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |    | UNIT-I                                                                                                                                                                                                                |     |

| l | a) | Generate a Hamming Code for the given 4-bit message word 1001 and rewrite the                                                                                                                                         | [7M |

|   | b) | entire message in Hamming Code.<br>Obtain the truth table of the function, and express function in sum-of-minterms<br>and product of max terms $Y (xy + z)(y + xz)$ .<br><b>Or</b>                                    | [7M |

|   | a) | For the Function $F = xy'z + x'y'z + w'xy + wx'y + wxy$ , draw the logic diagram using original Boolean expression and also for simplified expression. Compare the total number of gates for the two.                 | [7M |

|   | b) | Convert the given number "B2FA" to binary and Find the 2's complement of the result?                                                                                                                                  | [7N |

|   |    | UNIT-II                                                                                                                                                                                                               |     |

|   | a) | Simplify the Boolean function, using five-variable maps<br>F(A,B,C,D,E)=A'B'CE'+B'C'D'E'+A'B'D'+B'CD'+A'CD+A'BD                                                                                                       | [7N |

|   | b) | Design a full-subtractor circuit with three inputs $x,y$ , $B_{in}$ and two outputs <i>Diff</i> and $B_{out}$ . Where $B_{in}$ is the input borrow, $B_{out}$ is the output borrow and <i>Diff</i> is the difference. | [7N |

|   |    | Or                                                                                                                                                                                                                    |     |

|   | a) | Draw a logic diagram using only two-input NOR gates to implement the following function: $F(A,B,C,D) = (A \oplus B)'(C \oplus D)$                                                                                     | [7N |

|   | b) | Design the Excess-3 code adder circuit.                                                                                                                                                                               | [7N |

|   |    | UNIT-III                                                                                                                                                                                                              |     |

|   | a) | Implement the following logic function with 2n X1 multiplexer, where n is the number of variables in the function. $F(A, B, C, D) = S(4, 5, 6, 7, 8, 13, 14, 15)$ .                                                   | [7N |

|   | b) | Why does a carry look-a-head generator give a fast adder? How much is the speed up for an 8-stage circuit? Explain.                                                                                                   | [7N |

|   |    | Or                                                                                                                                                                                                                    |     |

|   | a) | What is a difference between a decoder and a digital demultiplexer? Explain their truth table differences by taking an example.                                                                                       | [7N |

|   | b) | Construct a 4 X16 decoder using two 3 X 8 decoder modules and additional logic.<br>Show the schematic diagram neatly.<br>UNIT-IV                                                                                      | [7N |

|   | a) | How does a SR latch differ from a gated RS latch?                                                                                                                                                                     | [7N |

|   | b) | Write the count sequence of 3-bit binary ripple counter. Design a 3-bit ripple counter using J-K flip-flops                                                                                                           | [7N |

|   |    | Or                                                                                                                                                                                                                    |     |

|"|"|||"|"|||||

- 8 a) Design a 4-bit binary UP/DOWN ripple counter with a control input for UP/DOWN [7M] counting

- b) Design a PIPO, which is a 4-bit buffer register with parallel in (loading) and parallel [7M] output (storing)

#### UNIT-V

- 9 a) Write difference between Mealy and Moore machines in detail. [7M]

- b) Design a sequential circuit for the state Table using D flip-flops. Assume twoinputs [7M] are A and B, output of the sequential circuit is O, present state of D flip-flops =  $Q_1Q_0$ , Next State of D flip-flops =  $(Q_1 * Q_0 *)$ .

|                    | Inputs (AB)                                 |      |      |      |  |  |

|--------------------|---------------------------------------------|------|------|------|--|--|

| Present            | 00                                          | 01   | 10   | 11   |  |  |

| state( $Q_1 Q_0$ ) |                                             |      |      |      |  |  |

| 00                 | 01/0                                        | 00/0 | 00/0 | 01/0 |  |  |

| 01                 | 10/1                                        | 00/1 | 00/1 | 10/1 |  |  |

| 10                 | 11/0                                        | 00/0 | 00/0 | 11/0 |  |  |

| 11                 | 01/1                                        | 00/1 | 00/1 | 01/1 |  |  |

|                    | Next State $(Q_1^* Q_0^*)/\text{Output}(O)$ |      |      |      |  |  |

#### Or

- 10 a) A sequential circuit has two inputs X and CLOCK and one output O. Incoming data [7M] are examined in consecutive groups of three digits and the output O=1 for the following three input sequences 000, 010 and 111. Draw a state diagram and implement the sequential circuit using J-K flip-flops.

- b) Define Finite state machine for the state table using D Flip-Flops.

[7M]

|               |                            | Input | s (AB) |    |

|---------------|----------------------------|-------|--------|----|

| Present state | 00                         | 01    | 10     | 11 |

| $(Q_1Q_0)$    |                            |       |        |    |

| 00            | 01                         | 00    | 00     | 01 |

| 01            | 10                         | 00    | 00     | 10 |

| 10            | 11                         | 00    | 00     | 11 |

| 11            | 01                         | 00    | 00     | 01 |

|               | Next State $(Q_1 * Q_0 *)$ |       |        |    |